# ISD ChipCorder® ISD15100 Series DataSheet

The information described in this document is the exclusive intellectual property of Nuvoton Technology Corporation and shall not be reproduced without permission from Nuvoton.

Nuvoton is providing this document only for reference purposes of Audio Product Line based system design. Nuvoton assumes no responsibility for errors or omissions.

All data and specifications are subject to change without notice.

For additional information or questions, please contact: Nuvoton Technology Corporation. <u>www.nuvoton.com</u>

# **TABLE OF CONTENTS**

| 1 GENERAL DESCRIPTION                       | 3  |

|---------------------------------------------|----|

| 2 FEATURES                                  |    |

| 3 BLOCK DIAGRAM                             |    |

| 4 PINOUT CONFIGURATION                      |    |

| 5 PIN DESCRIPTION                           |    |

| 6 ELECTRICAL CHARACTERISTICS                |    |

| 6.1 ABSOLUTE MAXIMUM RATINGS                |    |

| 6.2 OPERATING CONDITIONS                    |    |

| 6.3 DC PARAMETERS                           |    |

| 6.4 AC PARAMETERS                           |    |

| 6.4.1 Internal Oscillator                   |    |

| 6.4.2 Inputs                                |    |

| 6.4.3 Outputs                               |    |

| 6.4.4 SPI Timing                            |    |

| 6.4.5 I2S Timing                            |    |

| 7 APPLICATION DIAGRAM                       |    |

| 8 PACKAGE SPECIFICATION                     |    |

| 8.1 48 LEAD LQFP(7x7x1.4mm footprint 2.0mm) |    |

|                                             |    |

| 9 ORDERING INFORMATION                      | 19 |

| 10 REVISION HISTORY                         | 20 |

| IMPORTANT NOTICE                            | 21 |

#### 1 GENERAL DESCRIPTION

The ISD15100 series is a multi-message ChipCorder® featuring digital compression, comprehensive memory management, flash storage, and integrated analog/digital audio signal paths. The message management feature is designed to make message recording simple and address-free as well as make code development easier for playback-only applications. This family utilizes flash memory to provide non-volatile audio record/playback with durations up to 8 minutes for a single-chip solution. Unlike other ChipCorder series, the ISD15100 series provides an I²S digital audio interface, faster digital recording, higher sampling frequency, and a signal path with SNR equivalent to 12bit resolution.

The ISD15100 series can take digital audio data via I<sup>2</sup>S or SPI interface. When I<sup>2</sup>S input is selected, it will replace the analog audio inputs and will support sample rates of 32, 44.1 or 48 kHz depending upon clock configuration. When SPI interface is chosen, the sample rate of the audio data sent must be one of the ISD15100 supported sample rates.

The ISD15100 series has built-in analog audio inputs, analog audio line driver, and speaker driver output. The two analog audio inputs to the device are: (1) AUXIN has a fixed gain configured by SPI command, and (2) ANAIN/ANAOUT has a fixed gain amplifier with the gain set by two external resistors. ANAIN/ANAOUT can also be used as a microphone differential input (ANAIN/ANAOUT becomes MIC+/MIC-) in conjunction with an automatic gain control (AGC) circuit configured by SPI command. Analog outputs are available in three forms: (1) AUXOUT is a single-ended voltage output; (2) AUDOUT can be configured as either a single-ended voltage output or a single-ended current output; (3) BTL (bridge-tied-load) is a differential voltage output.

#### 2 FEATURES

- Fast Digital Programming

- Programming rate can go up to 1Mbits/second mainly limited by the flash memory write rate

- Duration

- 2 to 8 minutes based on 8kHz/4bit ADPCM

- Message Management

- Perform address-free recording: The ISD15100 allocates memory for new recording requests and upon completion, returns a start address to the host via SPI interface

- o Store pre-recorded audio (Voice Prompts) using high quality digital compression

- Use a simple index based command for playback

- Execute pre-programmed macro scripts (Voice Macros) designed to control the configuration of the device and play back Voice Prompts sequences and message recordings

- Sample Rate

- Seven record and playback sampling frequencies are available for a given master sample rate. For example, the record and playback sampling frequencies of 4, 5.3, 6.4, 8, 12.8, 16 and 32kHz\* are available when the device is clocked at a 32kHz master sample rate

- For I<sup>2</sup>S operation, 32, 44.1 and 48kHz master sample rates are available with record and playback sampling frequencies scaling accordingly

- · Compression Algorithms

- For recording

- ADPCM: 2, 3, 4 or 5 bits per sample

- µ-Law: 6, 7 or 8 bits per sample

- Differential μ-Law: 6, 7 or 8 bits per sample

- PCM: 8, 10 or 12 bits per sample. Each sampled value is stored as a code, offering no compression but preserving maximum resolution

- o For Pre-Recorded Voice Prompts

- μ-Law: 6, 7 or 8 bits per sample

- Differential µ-Law: 6, 7 or 8 bits per sample

- PCM: 8, 10 or 12 bits per sample

- Enhanced ADPCM: 2, 3, 4 or 5 bits per sample

- Variable-bit-rate optimized compression. This allows best possible compression given a

#### metric of SNR and background noise levels

#### Oscillator

- o Internal oscillator with internal reference: 2.048 MHz with ±10% deviation

- Internal oscillator with external resistor: 2.048 MHz with ±5% deviation when Rosc is 80k-ohm

- o External crystal or clock input

- I<sup>2</sup>S bit clock input

- Crystals and resonators support standard audio sampling rates of 2.048, 4.096, 8.192, 12.288 and11.2896MHz

#### Inputs

- AUXIN: Analog input with 2-bit gain control configured by SPI command

- ANAIN/ANAOUT:

- Analog input with the gain set by two external resistors from ANAOUT to ANAIN, or

- Microphone differential input (ANAIN/ANAOUT becomes MIC+/MIC-)

- Digital AGC:

- Automatic gain control of digitized data from the analog input

#### Outputs

- PWM: Class D speaker driver which can deliver typical output power:

- 8Ω load: 350mW @3.3V, 420mW @3.6V 8Ω load

- 4Ω load: 520mW @3.3V, 620mW @3.6V 8Ω load

- AUDOUT: configurable as a current or voltage single-ended line driver

- o AUXOUT: a single-ended voltage output

- o BTL: differential voltage output which can deliver typical output power:

- 63mW for  $8\Omega$  load, 115mW for  $4\Omega$  load

#### I/Os

- o SPI interface: MISO, MOSI, SCLK, SSB for commands and digital audio data

- o I2S interface: I2S CLK, I2S WS, I2S SDI, I2S SDO for digital audio data

- o 8 GPIO pins (4 of the 8 GPIO pins share with I2S)

- Three 8-bit Volume Control set by SPI command for flexible mixing

- VOLA: volume control for the digital audio data from I<sup>2</sup>S or analog inputs

- VOLB: volume control for the digital audio data from decompression block or SPI

- o VOLC: master volume control for PWM, AUDOUT, AUXOUT and I2S outputs

- Operating Voltage: 2.7-3.6V

- Standby Current: 1uA typical

- Package:

- o LQFP-48

- o Package is Halogen-free, RoHS-compliant and TSCA-compliant

- Temperature Options:

- o -40°C ~ 85°C

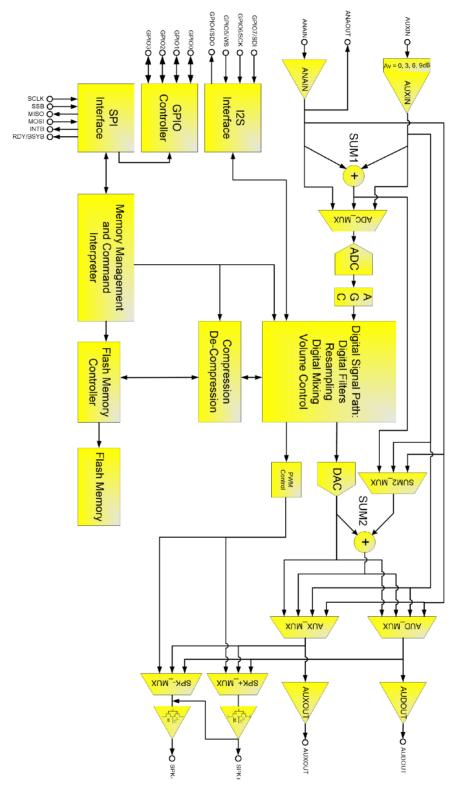

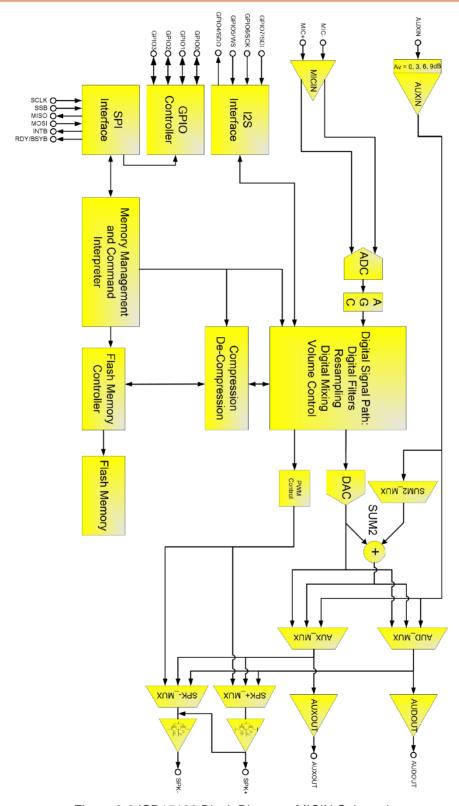

# 3 BLOCK DIAGRAM

Figure 3-1 ISD15100 Block Diagram, ANAIN Selected

Figure 3-2 ISD15100 Block Diagram, MICIN Selected

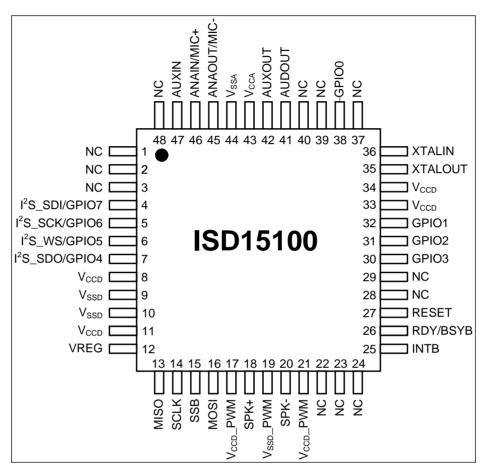

# 4 PINOUT CONFIGURATION

Figure 4-1 ISD15100 48-Lead LQFP Pin Configuration.

# **5 PIN DESCRIPTION**

| Pin<br>Number | Pin Name                       | I/O | Function                                                                                                                                                                                                                                                                                                                         |

|---------------|--------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | NC                             |     | This pin should be left unconnected.                                                                                                                                                                                                                                                                                             |

| 2             | NC                             |     | This pin should be left unconnected.                                                                                                                                                                                                                                                                                             |

| 3             | NC                             |     | This pin should be left unconnected.                                                                                                                                                                                                                                                                                             |

| 4             | I <sup>2</sup> S_SDI/<br>GPIO7 | I   | Serial Data Input of the I <sup>2</sup> S interface (If I2S is not used, this pin should be grounded).  Or, can be configured as a GPIO pin.                                                                                                                                                                                     |

| 5             | I <sup>2</sup> S_SCK/<br>GPIO6 | I/O | Clock input in slave mode or clock output in master mode. This pin can be configured as an external clock buffer if I <sup>2</sup> S is not used (If I2S is not used, this pin should be grounded).  Or, can be configured as a GPIO pin.                                                                                        |

| 6             | I <sup>2</sup> S_WS/<br>GPIO5  | I/O | Word Select (WS) input in slave mode or WS output in master mode (If I2S is not used, this pin should be grounded). Or, can be configured as a GPIO pin.                                                                                                                                                                         |

| 7             | I <sup>2</sup> S_SDO/<br>GPIO4 | 0   | Serial Data Output of the I <sup>2</sup> S Interface (If I2S is not used, this pin should be left unconnected).  Or, can be configured as a GPIO pin.                                                                                                                                                                            |

| 8             | Vccd                           | I   | Digital power supply.                                                                                                                                                                                                                                                                                                            |

| 9             | V <sub>SSD</sub>               | ı   | Digital Ground.                                                                                                                                                                                                                                                                                                                  |

| 10            | V <sub>SSD</sub>               | I   | Digital Ground.                                                                                                                                                                                                                                                                                                                  |

| 11            | Vccd                           | ı   | Digital power supply.                                                                                                                                                                                                                                                                                                            |

| 12            | VREG                           | 0   | A 1.8V regulator to supply the internal logic. A 0.1uF capacitor should be connected to this pin for supply decoupling and stability.                                                                                                                                                                                            |

| 13            | MISO                           | 0   | Master-In-Slave-Out. Serial output from the ISD15100 to the host. This pin is in tri-state when SSB=1.                                                                                                                                                                                                                           |

| 14            | SCLK                           | ı   | Serial Clock input to the ISD15100 from the host.                                                                                                                                                                                                                                                                                |

| 15            | SSB                            | l   | Slave Select input to the ISD15100 from the host. When SSB is low device is selected and responds to commands on the SPI interface.                                                                                                                                                                                              |

| 16            | MOSI                           | I   | Master-Out-Slave-In. Serial input to the ISD15100 from the host.                                                                                                                                                                                                                                                                 |

| 17            | Vccd_PWM                       | I   | Digital Power for the PWM Driver.                                                                                                                                                                                                                                                                                                |

| 18            | SPK+                           | 0   | PWM driver positive output. This SPK+ output, together with SPK- pin, provide a differential output to drive $8\Omega$ speaker. During power down this pin is in tri-state. Or, can be configured as BTL which, together with SPK- pin, provide a differential voltage output. Or, can independently switch to AUDOUT or AUXOUT. |

| 19            | Vssd_PWM                       | ı   | Digital Ground for the PWM Driver.                                                                                                                                                                                                                                                                                               |

| 20            | SPK-                           | Ο   | PWM driver negative output. This SPK- output, together with SPK+ pin, provides a differential output to drive $8\Omega$ speake. During power down this pin is tri-state.                                                                                                                                                         |

| Pin<br>Number | Pin Name         | I/O | Function                                                                                                                                                                                                                                                                                                                                             |

|---------------|------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               |                  |     | Or, can be configured as BTL which, together with SPK+ pin, provide a differential voltage output.                                                                                                                                                                                                                                                   |

|               |                  |     | Or, can independently switch to AUDOUT or AUXOUT.                                                                                                                                                                                                                                                                                                    |

| 21            | Vccd_PWM         |     | Digital Power for the PWM Driver.                                                                                                                                                                                                                                                                                                                    |

| 22            | NC               |     | This pin should be left unconnected.                                                                                                                                                                                                                                                                                                                 |

| 23            | NC               |     | This pin should be left unconnected.                                                                                                                                                                                                                                                                                                                 |

| 24            | NC               |     | This pin should be left unconnected.                                                                                                                                                                                                                                                                                                                 |

| 25            | INTB             | 0   | Active low interrupt request pin. This pin is an open-drain output.                                                                                                                                                                                                                                                                                  |

| 26            | RDY/BSYB         | 0   | An output pin to report the status of data transfer on the SPI interface. "High" indicates that ISD15100 is ready to accept new SPI commands or data.                                                                                                                                                                                                |

| 27            | RESET            | I   | Applying power to this pin will reset the chip. (A high pulse of 50ms or more will reset the chip.)                                                                                                                                                                                                                                                  |

| 28            | NC               |     | This pin should be left unconnected.                                                                                                                                                                                                                                                                                                                 |

| 29            | NC               |     | This pin should be left unconnected.                                                                                                                                                                                                                                                                                                                 |

| 30            | GPIO3            | I/O | GPIO                                                                                                                                                                                                                                                                                                                                                 |

| 31            | GPIO2            | I/O | GPIO                                                                                                                                                                                                                                                                                                                                                 |

| 32            | GPIO1            | I/O | GPIO                                                                                                                                                                                                                                                                                                                                                 |

| 33            | Vccd             | I   | Digital power supply pin.                                                                                                                                                                                                                                                                                                                            |

| 34            | V <sub>CCD</sub> | I   | Digital power supply pin.                                                                                                                                                                                                                                                                                                                            |

| 35            | XTALOUT          | 0   | Crystal interface output pin.                                                                                                                                                                                                                                                                                                                        |

| 36            | XTALIN           | I   | The CLK_CFG register determines one of the following three configurations: (1) A crystal or resonator connected between the XTALOUT and XTALIN pins. (2) A resistor connected to GND as a reference current to the internal oscillator and left the XTALOUT unconnected. (3) An external clock input to the device and left the XTALOUT unconnected. |

| 37            | NC               |     | This pin should be left unconnected.                                                                                                                                                                                                                                                                                                                 |

| 38            | GPIO0            | I/O | GPIO                                                                                                                                                                                                                                                                                                                                                 |

| 39            | NC               |     | This pin should be left unconnected.                                                                                                                                                                                                                                                                                                                 |

| 40            | NC               |     | This pin should be left unconnected.                                                                                                                                                                                                                                                                                                                 |

| 41            | AUDOUT           | 0   | Audio Out. This pin can be either a voltage output or a current output configured by the internal registers via SPI command.  If AUDOUT is not used, this pin should be left unconnected.                                                                                                                                                            |

| 42            | AUXOUT           | 0   | Aux Out. This pin is an analog voltage output.  If AUXOUT is not used, this pin should be left unconnected.                                                                                                                                                                                                                                          |

| 43            | Vcca             | ı   | Analog power supply pin.                                                                                                                                                                                                                                                                                                                             |

| 44            | V <sub>SSA</sub> |     | Analog ground pin.                                                                                                                                                                                                                                                                                                                                   |

| 45            | ANAOUT/          | 0   | Variable gain analog output with the gain set by feedback resistance to                                                                                                                                                                                                                                                                              |

| Pin<br>Number | Pin Name       | I/O | Function                                                                                                                                                                                         |

|---------------|----------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | MIC-           |     | ANAIN. Or, can be configured as MIC- which, together with MIC+, provides a microphone differential input. If ANAIN/ANAOUT is not used, this pin should be left unconnected.                      |

| 46            | ANAIN/<br>MIC+ | I   | Variable gain analog input. Or, can be configured as MIC+ which, together with MIC-, provides a microphone differential input. If ANAIN/ANAOUT is not used, this pin should be left unconnected. |

| 47            | AUXIN          | I   | Auxiliary input with the gain set by SPI command If AUXIN is not used, this pin should be left unconnected.                                                                                      |

| 48            | NC             |     | This pin should be left unconnected.                                                                                                                                                             |

## 6 ELECTRICAL CHARACTERISTICS

#### 6.1 ABSOLUTE MAXIMUM RATINGS

## ABSOLUTE MAXIMUM RATINGS (PACKAGED PARTS)[1]

| CONDITIONS                                                     | VALUES                                 |

|----------------------------------------------------------------|----------------------------------------|

| Junction temperature                                           | 130°C                                  |

| Storage temperature range                                      | -65°C to +150°C                        |

| Voltage Applied to any pins                                    | (Vss - 0.3V) to (Vcc + 0.3V)           |

| Voltage applied to any pin (Input current limited to +/-20 mA) | $(V_{SS} - 1.0V)$ to $(V_{CC} + 1.0V)$ |

| Power supply voltage to ground potential                       | -0.3V to +5.0V                         |

Stresses above those listed may cause permanent damage to the device. Exposure to the absolute maximum ratings may affect device reliability. Functional operation is not implied at these conditions.

## 6.2 OPERATING CONDITIONS

# **OPERATING CONDITIONS (INDUSTRIAL PACKAGED PARTS)**

| CONDITIONS                                     | VALUES                                             |

|------------------------------------------------|----------------------------------------------------|

| Operating temperature range (Case temperature) | -40°C to +85°C                                     |

| Supply voltage (V <sub>DD</sub> ) [1]          | +2.7V to +3.6V                                     |

| Ground voltage (Vss) [2]                       | oV                                                 |

| Input voltage (V <sub>DD</sub> ) [1]           | 0V to 3.6V                                         |

| Voltage applied to any pins                    | (V <sub>SS</sub> -0.3V) to (V <sub>DD</sub> +0.3V) |

NOTES: [1]  $V_{DD} = V_{CCA} = V_{CCD} = V_{CCPWM}$

$^{[2]}V_{SS} = V_{SSA} = V_{SSD} = V_{SSPWM}$

#### 6.3 DC PARAMETERS

| PARAMETER               | SYMBOL                 | MIN                 | TYP [1] | MAX                 | UNITS | CONDITIONS                                                 |

|-------------------------|------------------------|---------------------|---------|---------------------|-------|------------------------------------------------------------|

| Supply Voltage          | $V_{DD}$               | 2.7                 |         | 3.6                 | V     |                                                            |

| Input Low Voltage       | VIL                    | Vss-0.3             |         | 0.3xV <sub>DD</sub> | V     |                                                            |

| Input High Voltage      | ViH                    | 0.7xV <sub>DD</sub> |         | V <sub>DD</sub>     | V     |                                                            |

| Output Low Voltage      | Vol                    | Vss-0.3             |         | 0.3xV <sub>DD</sub> | V     | I <sub>OL</sub> = 1mA                                      |

| Output High Voltage     | Vон                    | 0.7xV <sub>DD</sub> |         | V <sub>DD</sub>     | V     | I <sub>OH</sub> = -1mA                                     |

| INTB Output Low Voltage | V <sub>OH1</sub>       |                     |         | 0.4                 | V     |                                                            |

| Record Current          | I <sub>DD_Record</sub> |                     |         | 40                  | mA    | V <sub>DD</sub> = 3.6V, No load,<br>Sampling freq = 16 kHz |

| Playback Current        | IDD_Playback           |                     |         | 30                  | mA    |                                                            |

| Standby Current         | I <sub>SB</sub>        |                     | 1       | 10                  | μΑ    | V <sub>DD</sub> = 3.6V                                     |

| Input Leakage Current   | lıL                    |                     |         | ±1                  | μΑ    | Force V <sub>DD</sub>                                      |

Notes:

## 6.4 AC PARAMETERS

#### 6.4.1 Internal Oscillator

| PARAMETER                                      | SYMBOL | MIN  | TYP          | MAX      | UNITS | CONDITIONS                                                         |

|------------------------------------------------|--------|------|--------------|----------|-------|--------------------------------------------------------------------|

| Internal Oscillator with internal reference    | FINT   | -10% | 2.048<br>MHz | +10<br>% | MHz   | Vdd = 3V.<br>At room temperature                                   |

| Internal Oscillator with external resistor [1] | Fext   | -5%  | 2.048<br>MHz | +5%      | MHz   | With 1% precision resistor, 80k-ohm. Vdd = 3V. At room temperature |

Notes:

#### **6.4.2** Inputs

#### **ANAIN & MICIN**

| PARAMETER                  | SYMBOL               | MIN | TYP [1] | MAX | UNITS | CONDITIONS                  |

|----------------------------|----------------------|-----|---------|-----|-------|-----------------------------|

| ANAIN Input Voltage        | Vanain               |     | 10-1000 |     | mV    | Peak-to-Peak[2]             |

| ANAIN Feed Back Resistance | R <sub>ANA(FB)</sub> | 40  |         | 100 | ΚΩ    |                             |

| MICIN Input Voltage        | VMICIN               |     | 5-500   |     | mV    | Peak-to-Peak <sup>[2]</sup> |

Notes:

<sup>&</sup>lt;sup>[1]</sup> Conditions V<sub>DD</sub>=3V, T<sub>A</sub>=25°C unless otherwise stated

<sup>&</sup>lt;sup>[1]</sup> Characterization data shows that frequency deviation is +/- 5% across temperature and voltage ranges.

<sup>[1]</sup> Conditions V<sub>DD</sub>=3V, T<sub>AB</sub>=25°C unless otherwise stated

<sup>[2]</sup> Depends on Gain Setting

#### **AUXIN**

| PARAMETER                        | SYMBOL                  | MIN  | TYP <sup>[1]</sup> | MAX  | UNITS | CONDITIONS                      |

|----------------------------------|-------------------------|------|--------------------|------|-------|---------------------------------|

| AUXIN Input Voltage              | V <sub>AUXIN</sub>      |      | 1000               |      | mV    | Peak-to-Peak[2]                 |

| Gain from AUXIN to AUXOUT/ANAOUT | AAUXIN GAIN             |      | 0 to 9             |      | dB    | 4 Gain Steps of 3db each        |

| AUXIN Gain Accuracy              | A <sub>AUXIN</sub> (GA) | -0.5 |                    | +0.5 | dB    |                                 |

| AUXIN Input Resistance           | RAUXIN                  |      | 20-40              |      | ΚΩ    | Depending on AUXIN Gain Setting |

Notes:

$^{[1]}$  Conditions  $V_{DD}$ =3V,  $T_A$ =25 $^{\circ}$ C unless otherwise stated.

[2] With 0db Gain setting.

## 6.4.3 Outputs

#### **AUXOUT**

| PARAMETER                | SYMBOL                        | MIN | TYP <sup>[1]</sup> | MAX | UNITS | CONDITIONS                |

|--------------------------|-------------------------------|-----|--------------------|-----|-------|---------------------------|

| SINAD, AUXIN to AUXOUT   | SINAD <sub>AUXIN_AUXOUT</sub> |     | 80                 |     | dB    | Load 5K <sup>[2][3]</sup> |

| SINAD, ANAIN to AUXOUT   | SINADanain_auxout             |     | 80                 |     | dB    | Load 5K <sup>[2][3]</sup> |

| PSRR                     | PSRR <sub>AUXOUT</sub>        |     | -40                |     | dB    | [4]                       |

| DC Bias                  | VBIAS_AUXOUT                  |     |                    | 1.2 | V     |                           |

| Minimum Load Impedance   | R <sub>L</sub> (AUXOUT)       | 5   |                    |     | ΚΩ    |                           |

| Maximum Load Capacitance | C <sub>L(AUXOUT)</sub>        |     |                    | 0.1 | nF    |                           |

Notes:

<sup>[1]</sup> Conditions V<sub>DD</sub>=3V, T<sub>A</sub>=25°C unless otherwise stated.

[2] 1 Vpp 1KHz signal applied at AUXIN/ANAIN with 0db Gain setting.

[3] All measurements are C-message weighted.

[4] Measured with 1KHz, 100 mVpp sine wave applied to V<sub>CCA</sub> pins.

#### OUT

| PARAMETER                               | SYMBOL                   | MIN | TYP <sup>[1]</sup> | MAX | UNITS | CONDITIONS                |

|-----------------------------------------|--------------------------|-----|--------------------|-----|-------|---------------------------|

| SINAD, AUXIN to AUDOUT <sup>[5]</sup>   | SINADauxin_audout        |     | 80                 |     | dB    | Load 5K <sup>[2][3]</sup> |

| SINAD, ANAIN to AUDOUT <sup>[5]</sup>   | SINADanain_audout        |     | 80                 |     | dB    | Load 5K <sup>[2][3]</sup> |

| PSRR <sup>[5]</sup>                     | PSRRAUDOUT               |     | -40                |     | dB    | [4]                       |

| DC Bias <sup>[5]</sup>                  | V <sub>BIAS_AUDOUT</sub> |     |                    | 1.2 | V     |                           |

| Minimum Load Impedance <sup>[5]</sup>   | R <sub>L</sub> (AUDOUT)  | 5   |                    |     | ΚΩ    |                           |

| Maximum Load Capacitance <sup>[5]</sup> | C <sub>L</sub> (AUDOUT)  |     |                    | 0.1 | nF    |                           |

| Output Current [6]                      | laudout                  | 0   | 3                  | 6   | mA    | [2][6]                    |

Notes:

$^{[1]}$  Conditions  $V_{cc}$ =3V,  $T_A$ =25°C unless otherwise stated.

[2] 1 Vpp 1KHz signal applied at AUXIN/ANAIN with 0db Gain setting.

[3] All measurements are C-message weighted.

[4] Measured with 1Khz, 100 mVpp sine wave applied to V<sub>CCA</sub> pins.

[5] Configured as AUDOUT(Voltage Output).

[6] Configured as AUDOUT(Current Output).

## **SPEAKER OUTPUTS**

| PARAMETER               | SYMBOL                       | MIN | TYP <sup>[1]</sup> | MAX | UNITS | CONDITIONS                  |

|-------------------------|------------------------------|-----|--------------------|-----|-------|-----------------------------|

| SNR, AUXIN to SPK+/SPK- | SNR <sub>AUXIN_SPK</sub>     |     | 60                 |     | dB    | Load 150Ω <sup>[2][3]</sup> |

| SNR, ANAIN to SPK+/SPK- | SNR <sub>ANAIN_SPK</sub>     |     | 60                 |     | dB    | Load 150Ω <sup>[2][3]</sup> |

| Output Power            | P <sub>OUT_SPK</sub> VCC=3.0 |     |                    | 360 | mW    | Load 8Ω <sup>[2]</sup>      |

| THD, AUXIN to SPK+/SPK- | THD %                        |     | <1%                |     |       | Load 8Ω <sup>[2]</sup>      |

| Minimum Load Impedance  | R <sub>L(SPK)</sub>          | 4   | 8                  |     | Ω     |                             |

Notes:

#### **SPEAKER OUTPUT POWER**

Conditions:  $V_{CCD} = 3.3V$ , 16KHz sample rate, 12bit PCM,  $T_A = +25$ °C, 1kHz signal

| PARAMETER    | SYMBOL               | MODE            | MIN | TYP <sup>[1]</sup> | MAX | UNITS | CONDITIONS                       |

|--------------|----------------------|-----------------|-----|--------------------|-----|-------|----------------------------------|

| Output Power | P <sub>OUT_SPK</sub> | Class-D<br>PWM  |     | 350                |     | mW    | @ 3.3V, Load 8Ω, 0.4% THD        |

|              |                      |                 |     | 420                |     | mW    | @ 3.6V, Load 8Ω, 0.4% THD        |

|              |                      |                 |     | 520                |     | mW    | @ 3.3V, Load 4Ω, 0.8% THD        |

|              |                      |                 |     | 620                |     | mW    | @ 3.3V, Load 4Ω, 0.8% THD        |

|              |                      | Class-AB<br>BTL |     | 63                 |     | mW    | Load 8Ω, 0.1% THD <sup>[1]</sup> |

|              |                      |                 |     | 125                |     | mW    | Load 4Ω, 0.1% THD <sup>[1]</sup> |

Notes:

[1] CLASS AB BTL is fixed referenced from bandgap, independent from Vcca.

<sup>[1]</sup> Conditions V<sub>cc</sub>=3V, T<sub>A</sub>=25°C unless otherwise stated.

<sup>[2] 1</sup> Vpp 1KHz signal applied at AUXIN/ANAIN with 0db Gain setting.

<sup>[3]</sup> All measurements are C-message weighted.

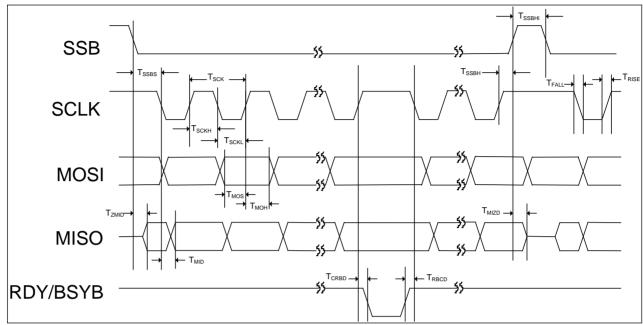

## 6.4.4 SPI Timing

Figure 6-1 SPI Timing

| SYMBOL            | DESCRIPTION                                               | MIN   | TYP | MAX  | UNIT |

|-------------------|-----------------------------------------------------------|-------|-----|------|------|

| Тѕск              | SCLK Cycle Time                                           | 60    |     |      | ns   |

| Тѕскн             | SCLK High Pulse Width                                     | 25    |     |      | ns   |

| T <sub>SCKL</sub> | SCLK Low Pulse Width                                      | 25    |     |      | ns   |

| T <sub>RISE</sub> | Rise Time for All Digital Signals                         |       |     | 10   | ns   |

| T <sub>FALL</sub> | Fall Time for All Digital Signals                         |       |     | 10   | ns   |

| T <sub>SSBS</sub> | SSB Falling Edge to 1st SCLK Falling Edge Setup Time      | 30    |     |      | ns   |

| Тѕѕвн             | Last SCLK Rising Edge to SSB Rising Edge Hold Time        | 30 ns |     | 50us |      |

| Тѕѕвні            | SSB High Time between SSB Lows                            |       |     |      | ns   |

| Тмоѕ              | MOSI to SCLK Rising Edge Setup Time                       |       |     |      | ns   |

| Тмон              | SCLK Rising Edge to MOSI Hold Time                        | 15    |     |      | ns   |

| T <sub>ZMID</sub> | Delay Time from SSB Falling Edge to MISO Active           |       |     | 12   | ns   |

| T <sub>MIZD</sub> | Delay Time from SSB Rising Edge to MISO Tri-state         |       |     | 12   | ns   |

| T <sub>MID</sub>  | Delay Time from SCLK Falling Edge to MISO                 |       |     | 12   | ns   |

| T <sub>CRBD</sub> | Delay Time from SCLK Rising Edge to RDY/BSYB Falling Edge |       |     | 12   | ns   |

| T <sub>RBCD</sub> | Delay Time from RDY/BSYB Rising Edge to SCLK Falling Edge | 0     |     |      | ns   |

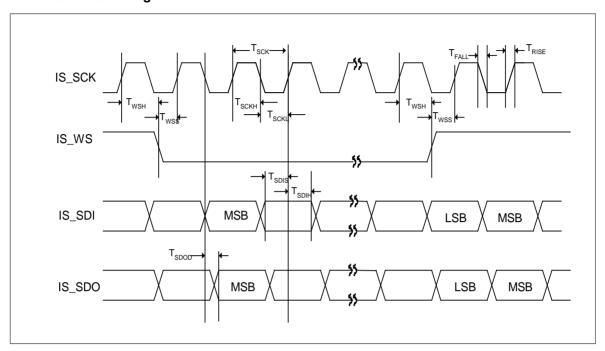

## **6.4.5 I2S Timing**

Figure 6-2 I<sup>2</sup>S Timing

| SYMBOL            | DESCRIPTION                                    | MIN | TYP | MAX | UNIT |

|-------------------|------------------------------------------------|-----|-----|-----|------|

| Тѕск              | IS_SCK Cycle Time                              | 60  |     |     | ns   |

| T <sub>SCKH</sub> | IS_SCK High Pulse Width                        | 25  |     |     | ns   |

| T <sub>SCKL</sub> | IS_SCK Low Pulse Width                         | 25  |     |     | ns   |

| T <sub>RISE</sub> | Rise Time for All Digital Signals              |     |     | 10  | ns   |

| T <sub>FALL</sub> | Fall Time for All Digital Signals              |     |     | 10  | ns   |

| T <sub>WSS</sub>  | WS to IS_SCK Rising Edge Setup Time            | 20  |     |     | ns   |

| Twsh              | IS_SCK Rising Edge to IS_WS Hold Time          | 20  |     |     | ns   |

| T <sub>SDIS</sub> | IS_SDI to IS_SCK Rising Edge Setup Time        |     |     |     | ns   |

| T <sub>SDIH</sub> | IS_SCK Rising Edge to IS_SDI Hold Time         | 15  |     |     | ns   |

| T <sub>SDOD</sub> | Delay Time from IS_SCLK Falling Edge to IS_SDO |     |     | 12  | ns   |

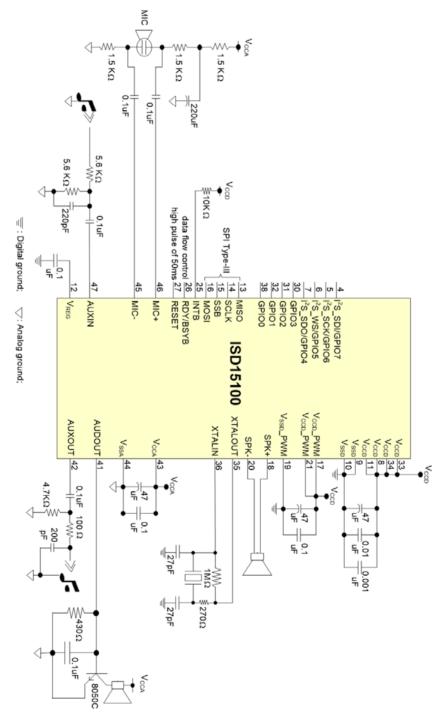

# 7 APPLICATION DIAGRAM

The following applications example is for references only. It makes no representation or warranty that such applications shall be suitable for the use specified. Each design has to be optimized in its own system for the best performance on voice quality, current consumption, functionalities and etc.

Figure 7-1 ISD15100 Application Diagram

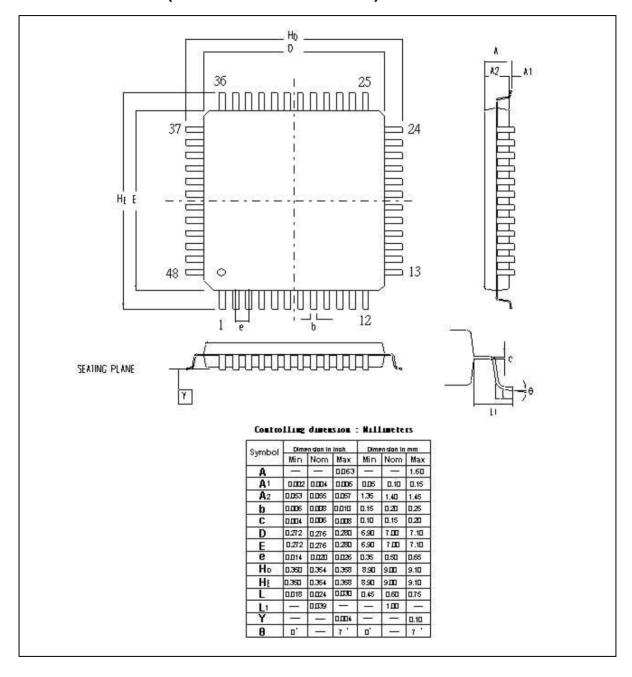

# 8 PACKAGE SPECIFICATION

# 8.1 48 LEAD LQFP(7x7x1.4MM FOOTPRINT 2.0MM)

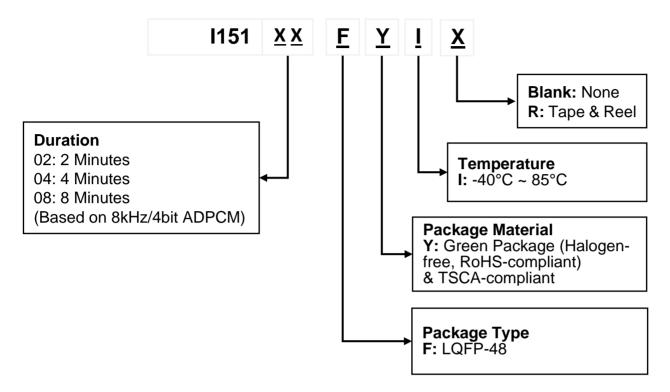

## 9 ORDERING INFORMATION

| Package Number | Part Number  | Ordering Number | Duration | Package                | Temperature  | Notes |

|----------------|--------------|-----------------|----------|------------------------|--------------|-------|

| ISD15102FYI    | ISD15102FYI  | I15102FYI       | 2min     | LQFP-48                | -40°C ~ 85°C |       |

| ISD15102FYIR   | ISD15102FYIR | I15102FYIR      | 2min     | LQFP-48<br>Tape & Reel | -40°C ~ 85°C |       |

| ISD15104FYI    | ISD15104FYI  | I15104FYI       | 4min     | LQFP-48                | -40°C ~ 85°C |       |

| ISD15104FYIR   | ISD15104FYIR | I15104FYIR      | 4min     | LQFP-48<br>Tape & Reel | -40°C ~ 85°C |       |

| ISD15108FYI    | ISD15108FYI  | I15108FYI       | 8min     | LQFP-48                | -40°C ~ 85°C |       |

| ISD15108FYIR   | ISD15108FYIR | I15108FYIR      | 8min     | LQFP-48<br>Tape & Reel | -40°C ~ 85°C |       |

# 10 REVISION HISTORY

| REVISION | DATE         | DESCRIPTION                                                               |

|----------|--------------|---------------------------------------------------------------------------|

| 1.0      | July 1, 2010 | Initial Release                                                           |

| 1.3      | May 6, 2011  | Add Absolute Maximum Ratings                                              |

| 1.4      | Aug 30, 2011 | Update register 0x19 ~ 0x1F description Update output power description   |

| 1.5      | Mar 25, 2020 | Update Document Format                                                    |

| 1.6      | Jun 15, 2021 | Update Ordering Information Update output power Remove buzzer description |

| 1.7      | Feb 1, 2023  | Update Halogen-free, RoHS-compliant and TSCA-compliant description        |

#### **IMPORTANT NOTICE**

Nuvoton Products are neither intended nor warranted for usage in systems or equipment, any malfunction or failure of which may cause loss of human life, bodily injury or severe property damage. Such applications are deemed, "Insecure Usage".

Insecure usage includes, but is not limited to: equipment for surgical implementation, atomic energy control instruments, airplane or spaceship instruments, the control or operation of dynamic, brake or safety systems designed for vehicular use, traffic signal instruments, all types of safety devices, and other applications intended to support or sustain life.

All Insecure Usage shall be made at customer's risk, and in the event that third parties lay claims to Nuvoton as a result of customer's Insecure Usage, customer shall indemnify the damages and liabilities thus incurred by Nuvoton.

Please note that all data and specifications are subject to change without notice.

All the trademarks of products and companies mentioned in this datasheet belong to their respective owners.